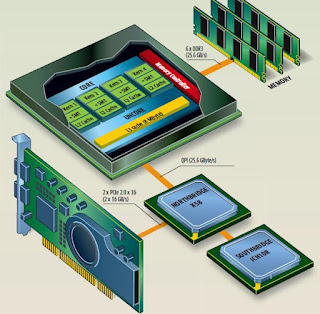

Fig 1 and fig 2 shows

architecture of processor “i7 and core to quad processor” respectively. By

comparing i7 processor with previous processors we can conclude that cores in

old processors shares there cache memory. This causes result in un efficient

utilization of resources (cache), because when one core accessing cache memory

then no other processor can access cache. He must have to wait until it is

released by core.

Fig

1.architecture of i7 processor

Fig 2.archtiecture of core

to quad processor

In i7 processor there is

an independent local L2 cache memory for each core. These cache accessed by

only their cores, not by others. Also there is one shared L3 cache memory of

size 8mb which is shared among all four cores of i7 processor. I just think

that shared memory is critical section area that means shared memory can be

used by only one core at a time, these results in decreasing system

performance.

Now I have an idea to

overcome this is dividing shared cache in 4 same size caches as shown in fig 3.

This result in when one core accessing an shared memory then other can access

other shared memory thus one core does not have to wait for other core to release

shared cache.

Above solution may causes

deadlock. So we have to force them to use only one shared memory at a time so

we can avoid deadlocks. But this approach will may result in program does not

fit in that much of size.

No comments:

Post a Comment